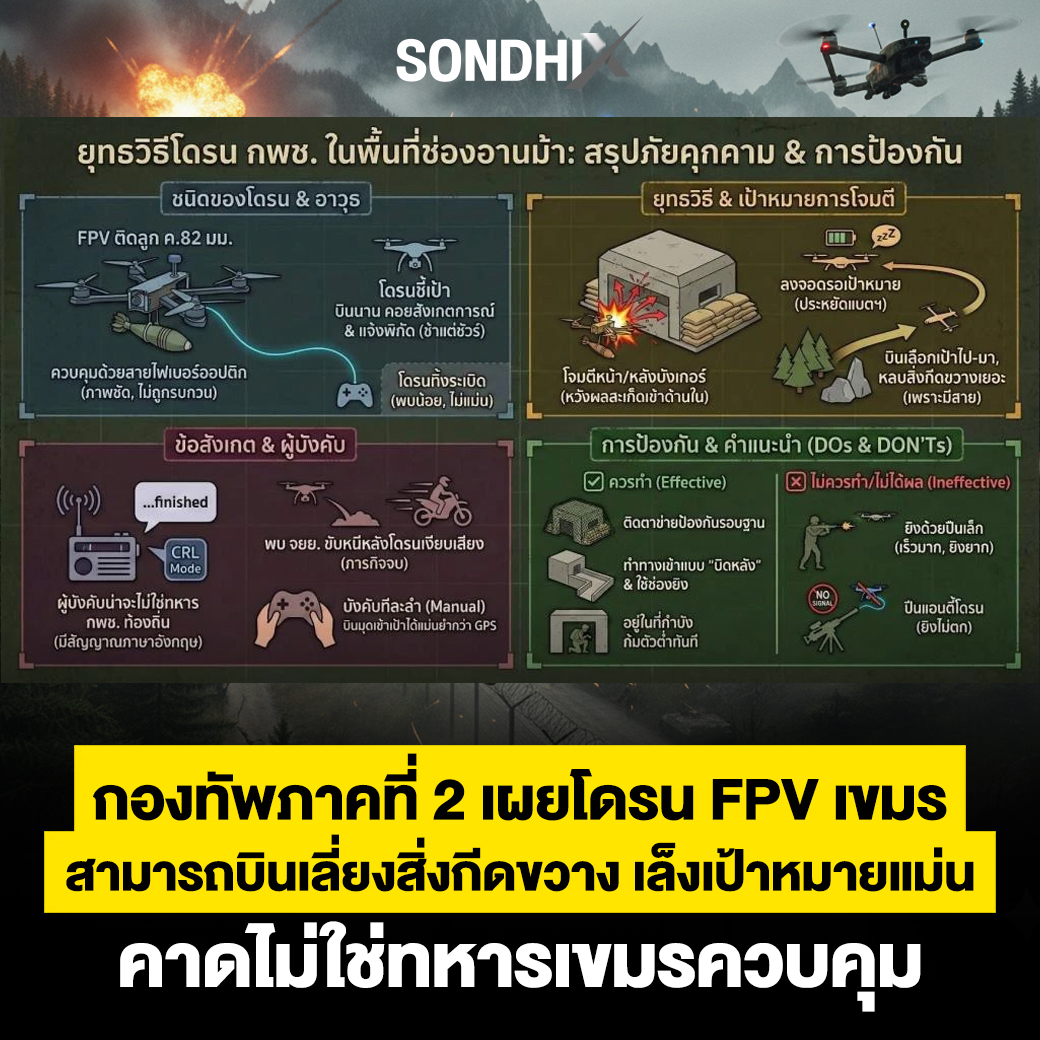

กองทัพภาคที่ 2 สรุปสถานการณ์ชายแดนวันส่งท้ายปี พื้นที่แนวหน้ายังคงนิ่ง กัมพูชายังคงรักษาระดับเตรียมพร้อม ปรับปรุงฐานที่มั่น พร้อมลำเลียงอาวุธ กระสุน และถุงยังชีพสู่หน้าแนว ฝ่ายไทยยังคงควบคุมพื้นที่และสถานการณ์โดยรวมได้

.

เมื่อเวลา 09.30 น. วันที่ 1 ม.ค. 2569 ศูนย์ปฏิบัติการ กองทัพภาคที่ 2 (ทภ.2) สรุปสถานการณ์ชายแดนไทย-กัมพูชา ช่วงวันที่ 31 ธ.ค. 2568 ปีที่ผ่านมา ภาพรวมตลอดแนวชายแดนยังคงสงบ แต่ยังไม่สามารถวางใจ พื้นที่หลักหลายจังหวัดไม่พบความเคลื่อนไหวผิดปกติ ขณะที่ฝ่ายกัมพูชายังคงเดินหน้าเสริมความแข็งแรงที่มั่นอย่างต่อเนื่อง ท่ามกลางการเฝ้าระวังอย่างใกล้ชิดของฝ่ายไทย

.

ชายแดนจังหวัดอุบลราชธานี-จังหวัดศรีสะเกษ เงียบทั้งแนว พื้นที่ช่องบกและช่องอานม้า จ.อุบลราชธานี ยังไร้สัญญาณเคลื่อนไหวสำคัญ

.

ด้าน จ.ศรีสะเกษ ตั้งแต่ช่องซำแต-โดนตวล-ภูผี-สัตตะโสม-พนมประสิทธิโส-ช่องตาเฒ่า รวมถึงแนวปราสาทพระวิหาร-ผามออีแดง-ห้วยตามาเรีย สถานการณ์ยังคงนิ่ง แม้กัมพูชาจะเฝ้าตรวจการณ์ปรับปรุงพื้นที่และการเคลื่อนย้ายกำลังของฝ่ายไทยอย่างใกล้ชิด

.

ชายแดนจังหวัดสุรินทร์-จังหวัดบุรีรัมย์ พื้นที่ปราสาทตาควาย-เนิน 350 และปราสาทตาเมือนธม จ.สุรินทร์ ไม่พบความเคลื่อนไหวเพิ่มเติม เช่นเดียวกับช่องจอม-ช่องระยี-ปลดต่าง และช่องสายตะกู จ.บุรีรัมย์ ที่ยังคงเงียบสงบ

.

ในพื้นที่ส่วนหลัง ฝ่ายกัมพูชายังคงดัดแปลงที่มั่น ซ่อมสายไฟ-สายสัญญาณ บรรจุดินใส่กระสอบ ขุดหลุมทำกำบัง ติดตั้งระบบสนับสนุน พร้อมลำเลียงอาวุธ กระสุน และถุงยังชีพสู่หน้าแนว โดยใช้รถจักรยานยนต์เป็นหลัก

.

ตลอดวันไม่พบการปะทะอาวุธหนักหรือการบุกรุกพื้นที่ ฝ่ายกัมพูชายังรักษาระดับเตรียมพร้อม เน้นเสริมที่มั่น ลำเลียงยุทโธปกรณ์ ควบคุมข้อมูลข่าวสาร และเฝ้าตรวจฝ่ายไทยอย่างใกล้ชิด ขณะที่ฝ่ายไทยยังคงควบคุมพื้นที่และสถานการณ์โดยรวมได้ในระดับดี

.

#Sondhitalk #คุยทุกเรื่องกับสนธิ #Thaitimes #SondhiX #สนธิเล่าเรื่อง #กัมพูชายิงก่อน #CambodiaOpenedFire #ไทยนี้รักสงบแต่ถึงรบไม่ขลาด

.

เมื่อเวลา 09.30 น. วันที่ 1 ม.ค. 2569 ศูนย์ปฏิบัติการ กองทัพภาคที่ 2 (ทภ.2) สรุปสถานการณ์ชายแดนไทย-กัมพูชา ช่วงวันที่ 31 ธ.ค. 2568 ปีที่ผ่านมา ภาพรวมตลอดแนวชายแดนยังคงสงบ แต่ยังไม่สามารถวางใจ พื้นที่หลักหลายจังหวัดไม่พบความเคลื่อนไหวผิดปกติ ขณะที่ฝ่ายกัมพูชายังคงเดินหน้าเสริมความแข็งแรงที่มั่นอย่างต่อเนื่อง ท่ามกลางการเฝ้าระวังอย่างใกล้ชิดของฝ่ายไทย

.

ชายแดนจังหวัดอุบลราชธานี-จังหวัดศรีสะเกษ เงียบทั้งแนว พื้นที่ช่องบกและช่องอานม้า จ.อุบลราชธานี ยังไร้สัญญาณเคลื่อนไหวสำคัญ

.

ด้าน จ.ศรีสะเกษ ตั้งแต่ช่องซำแต-โดนตวล-ภูผี-สัตตะโสม-พนมประสิทธิโส-ช่องตาเฒ่า รวมถึงแนวปราสาทพระวิหาร-ผามออีแดง-ห้วยตามาเรีย สถานการณ์ยังคงนิ่ง แม้กัมพูชาจะเฝ้าตรวจการณ์ปรับปรุงพื้นที่และการเคลื่อนย้ายกำลังของฝ่ายไทยอย่างใกล้ชิด

.

ชายแดนจังหวัดสุรินทร์-จังหวัดบุรีรัมย์ พื้นที่ปราสาทตาควาย-เนิน 350 และปราสาทตาเมือนธม จ.สุรินทร์ ไม่พบความเคลื่อนไหวเพิ่มเติม เช่นเดียวกับช่องจอม-ช่องระยี-ปลดต่าง และช่องสายตะกู จ.บุรีรัมย์ ที่ยังคงเงียบสงบ

.

ในพื้นที่ส่วนหลัง ฝ่ายกัมพูชายังคงดัดแปลงที่มั่น ซ่อมสายไฟ-สายสัญญาณ บรรจุดินใส่กระสอบ ขุดหลุมทำกำบัง ติดตั้งระบบสนับสนุน พร้อมลำเลียงอาวุธ กระสุน และถุงยังชีพสู่หน้าแนว โดยใช้รถจักรยานยนต์เป็นหลัก

.

ตลอดวันไม่พบการปะทะอาวุธหนักหรือการบุกรุกพื้นที่ ฝ่ายกัมพูชายังรักษาระดับเตรียมพร้อม เน้นเสริมที่มั่น ลำเลียงยุทโธปกรณ์ ควบคุมข้อมูลข่าวสาร และเฝ้าตรวจฝ่ายไทยอย่างใกล้ชิด ขณะที่ฝ่ายไทยยังคงควบคุมพื้นที่และสถานการณ์โดยรวมได้ในระดับดี

.

#Sondhitalk #คุยทุกเรื่องกับสนธิ #Thaitimes #SondhiX #สนธิเล่าเรื่อง #กัมพูชายิงก่อน #CambodiaOpenedFire #ไทยนี้รักสงบแต่ถึงรบไม่ขลาด

กองทัพภาคที่ 2 สรุปสถานการณ์ชายแดนวันส่งท้ายปี พื้นที่แนวหน้ายังคงนิ่ง กัมพูชายังคงรักษาระดับเตรียมพร้อม ปรับปรุงฐานที่มั่น พร้อมลำเลียงอาวุธ กระสุน และถุงยังชีพสู่หน้าแนว ฝ่ายไทยยังคงควบคุมพื้นที่และสถานการณ์โดยรวมได้

.

เมื่อเวลา 09.30 น. วันที่ 1 ม.ค. 2569 ศูนย์ปฏิบัติการ กองทัพภาคที่ 2 (ทภ.2) สรุปสถานการณ์ชายแดนไทย-กัมพูชา ช่วงวันที่ 31 ธ.ค. 2568 ปีที่ผ่านมา ภาพรวมตลอดแนวชายแดนยังคงสงบ แต่ยังไม่สามารถวางใจ พื้นที่หลักหลายจังหวัดไม่พบความเคลื่อนไหวผิดปกติ ขณะที่ฝ่ายกัมพูชายังคงเดินหน้าเสริมความแข็งแรงที่มั่นอย่างต่อเนื่อง ท่ามกลางการเฝ้าระวังอย่างใกล้ชิดของฝ่ายไทย

.

ชายแดนจังหวัดอุบลราชธานี-จังหวัดศรีสะเกษ เงียบทั้งแนว พื้นที่ช่องบกและช่องอานม้า จ.อุบลราชธานี ยังไร้สัญญาณเคลื่อนไหวสำคัญ

.

ด้าน จ.ศรีสะเกษ ตั้งแต่ช่องซำแต-โดนตวล-ภูผี-สัตตะโสม-พนมประสิทธิโส-ช่องตาเฒ่า รวมถึงแนวปราสาทพระวิหาร-ผามออีแดง-ห้วยตามาเรีย สถานการณ์ยังคงนิ่ง แม้กัมพูชาจะเฝ้าตรวจการณ์ปรับปรุงพื้นที่และการเคลื่อนย้ายกำลังของฝ่ายไทยอย่างใกล้ชิด

.

ชายแดนจังหวัดสุรินทร์-จังหวัดบุรีรัมย์ พื้นที่ปราสาทตาควาย-เนิน 350 และปราสาทตาเมือนธม จ.สุรินทร์ ไม่พบความเคลื่อนไหวเพิ่มเติม เช่นเดียวกับช่องจอม-ช่องระยี-ปลดต่าง และช่องสายตะกู จ.บุรีรัมย์ ที่ยังคงเงียบสงบ

.

ในพื้นที่ส่วนหลัง ฝ่ายกัมพูชายังคงดัดแปลงที่มั่น ซ่อมสายไฟ-สายสัญญาณ บรรจุดินใส่กระสอบ ขุดหลุมทำกำบัง ติดตั้งระบบสนับสนุน พร้อมลำเลียงอาวุธ กระสุน และถุงยังชีพสู่หน้าแนว โดยใช้รถจักรยานยนต์เป็นหลัก

.

ตลอดวันไม่พบการปะทะอาวุธหนักหรือการบุกรุกพื้นที่ ฝ่ายกัมพูชายังรักษาระดับเตรียมพร้อม เน้นเสริมที่มั่น ลำเลียงยุทโธปกรณ์ ควบคุมข้อมูลข่าวสาร และเฝ้าตรวจฝ่ายไทยอย่างใกล้ชิด ขณะที่ฝ่ายไทยยังคงควบคุมพื้นที่และสถานการณ์โดยรวมได้ในระดับดี

.

#Sondhitalk #คุยทุกเรื่องกับสนธิ #Thaitimes #SondhiX #สนธิเล่าเรื่อง #กัมพูชายิงก่อน #CambodiaOpenedFire #ไทยนี้รักสงบแต่ถึงรบไม่ขลาด